CIES Consortium

Industry-Academic Collaboration

Spintronics LSI Technology

R&D of material and device technologies

for STT/SOT-MRAM & spintronics/CMOS Hybrid processor

-

Research Director

Research Director

Prof.

Tetsuo Endoh -

Research Director

Research Director

Prof.

Shoji Ikeda

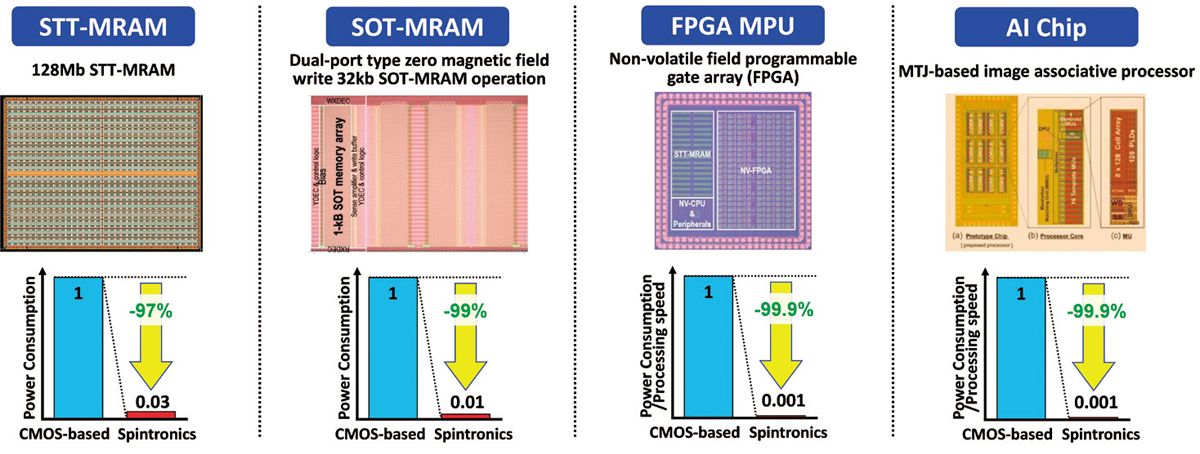

In this R&D project, the technologies for STT/SOT-MRAM & Spintronics/CMOS Hybrid processor are researched and developed with combing the spintronics technology and the silicon CMOS technology, in joint efforts between industry and academia.

The actual R&D items are as follows. ①Material/device technologies for the spintronics devices that have a compatibility for CMOS integrated circuits, ②Unit process/process integration technologies using the industry-standard 300mm Si wafers, ③Highly efficient measurement/evaluation technologies and multifunctional analysis technologies, ④Circuit and design tool technologies that cover from basic memory cells to large scale integrated circuits.

By integrating these developed technologies, we have designed STT/SOT-MRAM, and microcontrollers and AI application processors such as image recognition processors using spintronics/CMOS hybrid technology, and have demonstrated low power consumption performance in their integrated circuits prototyped using 300mm process lines. From now on, we will continue to promote further technological innovation through this project. In this way, we will accelerate the practical application of nonvolatile working memory and nonvolatile logic, which will realize dramatic low-power systems, and contribute to the realization of a carbon neutral society.