CIESコンソーシアム

産学共同研究

スピントロニクス LSI技術

STT/SOT-MRAM & スピントロニクス/CMOS Hybridプロセッサの研究開発

-

研究代表者

研究代表者

遠藤 哲郎 教授 -

研究代表者

研究代表者

池田 正二 教授

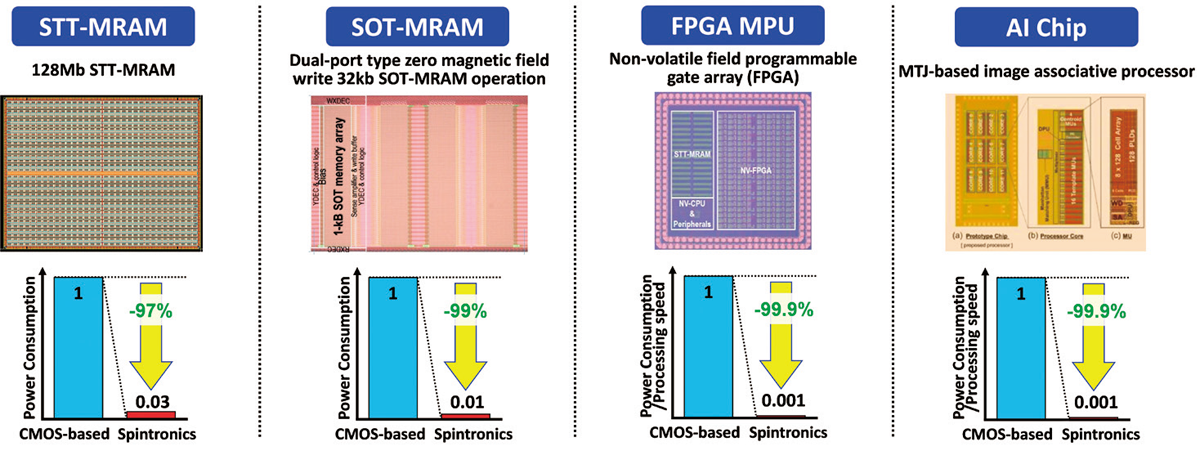

本テーマでは、スピントロニクス技術とシリコンCMOS技術の融合によるSTT-MRAM・SOT-MRAM及びスピントロニクス/CMOS Hybridアプリケーションプロセッサに関する技術を、産学が連携して研究開発しています。

具体的には、①CMOS集積回路と親和性の高いスピントロニクス素子の高性能化に向けた材料・デバイス技術、②産業界で標準の300mm Siウェハを用いたユニットプロセス・プロセスインテグレーション製造技術、③高効率な計測・評価技術、多機能的な分析技術、④基本メモリセルから大規模集積回路まで網羅する回路技術・設計ツールを一貫して研究開発しています。

これらの技術を統合集積化することにより、STT-MRAM・SOT-MRAM及びスピントロニクス/CMOS Hybrid技術を用いたマイコンや画像認識プロセッサなどのAIアプリケーションプロセッサを設計し、300mmプロセスラインを用いて試作を行い、これまでその低消費電力性能を実証してきており、今後も本研究開発を通じさらなる技術革新を進めていきます。これにより、飛躍的な省エネルギーシステムを実現する不揮発ワーキングメモリや不揮発ロジックなどの実用化を促進し、カーボンニュートラル社会の実現に貢献します。