CIES Consortium

Industry-Academic Collaboration

AI Hardware Circuit Technology

R&D of MTJ/CMOS Hybrid AI application processors

-

Prof.

Prof.

Tetsuo Endoh

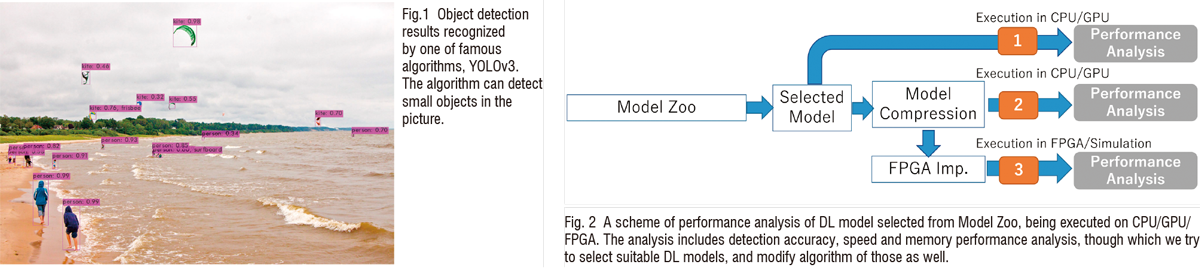

Advances in deep learning (DL) technology and parallel processors (e.g., GPUs) that can perform large-scale operations at high speed have made it possible to achieve highly accurate and fast object recognition, which was difficult until now (Figure 1). However, while these processors are capable of high-speed computation, they also consume a lot of power for accessing storage circuits, so it is necessary to reduce power consumption when installing them in in-vehicle computers and edge devices. Power consumption reduction can be expected by compressing and optimizing the DL algorithm. Furthermore, by applying power gating (PG), which takes advantage of the non-volatility of MTJ/CMOS hybrid circuits, power consumption reduction can be expected from power reduction during memory circuit access.

Therefore, we are developing a scheme to analyze the performance (recognition accuracy, speed, and memory access patterns) for DL algorithms running on various hardware (Figure 2). By analyzing memory patterns and improving algorithms suitable for PG, we aim to develop DL algorithms that match MTJ/CMOS hybrid circuit technology.