CIESコンソーシアム

産学共同研究

AIハードウェア 回路技術

MTJ/CMOS Hybrid AIアプリケーションプロセッサの研究開発

-

遠藤 哲郎 教授

遠藤 哲郎 教授

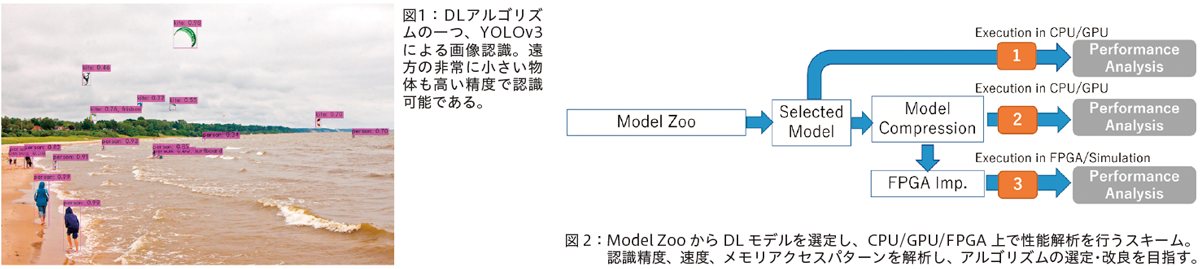

ディープラーニング(DL)の技術と大規模演算を高速に行うことのできる並列演算プロセッサ(GPUなど)の進歩により、これまで難しかった高精度かつ高速な物体認識が可能となってきました(図1)。しかし、これらのプロセッサは高速に演算できる反面、記憶回路へのアクセスに多くの電力を消費するため、車載コンピュータやエッジデバイスに搭載するには消費電力の削減が必要になります。DLアルゴリズムの圧縮・最適化を行うことで消費電力の削減が期待できますが、さらにMTJ/CMOS Hybrid 回路の不揮発性を利用したパワーゲーティング(PG)を適用することで、記憶回路アクセス時の電力削減から消費電力削減が期待できます。

そこで、様々なハードウェア上で動作するDLアルゴリズムに対し、その性能(認識精度、速度、メモリアクセスパターン)を解析するスキームの構築を行っています(図2)。メモリパターンを解析してPGに適したアルゴリズムの改良を行い、MTJ/CMOS Hybrid 回路技術にマッチしたDLアルゴリズムの開発を目指しています。