CIES Consortium

Industry-Academic Collaboration

AI Hardware Circuit Technology

R&D of error correction technologies in flexible information processing

-

Prof.

Prof.

Tetsuo Endoh

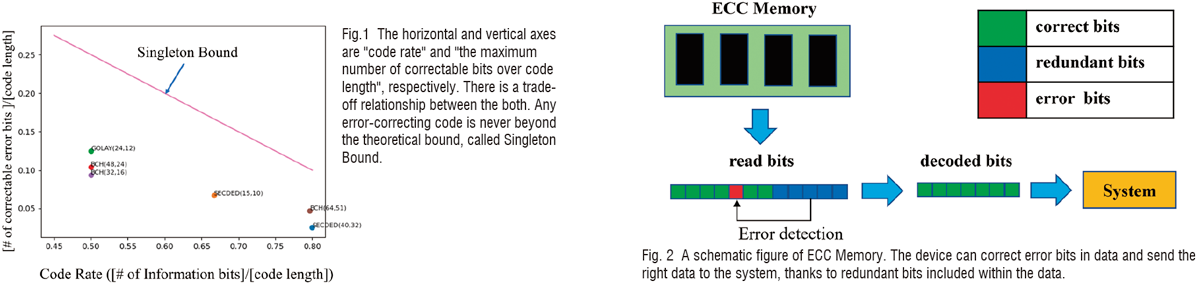

In DRAMs and other storage devices, cosmic rays, temperature conditions, and other factors can cause the storage bits to flip, resulting in incorrect calculation results. ECC (Error Correction Code) technology has been developed to detect and correct these errors, by converting the original data into an error correction code with redundancy, which can detect errors and restore the original data. However, in order to increase the correction capability (i.e., to detect and correct more errors), a large amount of redundancy is required to match the capability (Fig. 1).

ECC technology is also used in “memory”, an important component in computers, and in particular, memory that has an ECC circuit implemented as hardware is called ECC memory (Fig.2). Normally, the ECC algorithm called "SECDED", which is capable of correcting 1-bit errors and detecting 2-bit errors, has been commonly used in ECC memory. In this study, we have been exploring and verifying not only SECDED, but also the most suitable ECC algorithm with high correction capability for STT-MRAM based on software, which is easy to implement and improve by trial and error. The BCH code can select the number of bits that can be corrected under certain constraints. On the other hand, Golay codes can detect and correct errors and recover data with a simpler calculation than BCH codes, although the code length and the number of correctable bits are fixed.