CIES Consortium

National Projects

JST ACCEL Project

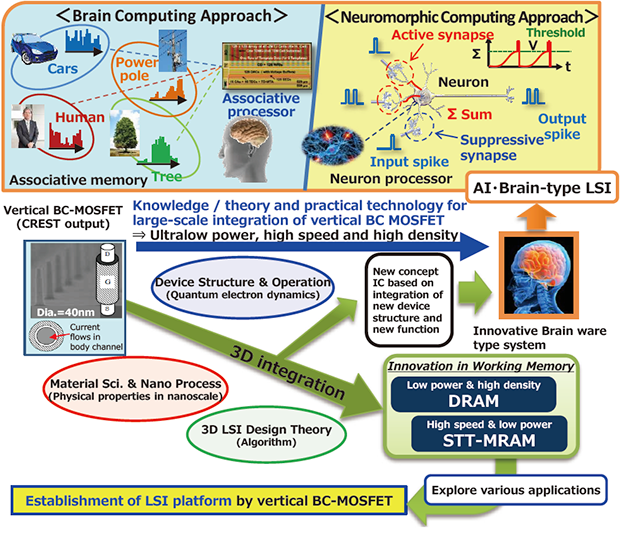

Three-dimensional integrated circuits technology based on vertical BC-MOSFET and its advanced application exploration

-

Research Director

Research Director

Prof.

Tetsuo Endoh -

Program Manager

Program Manager

Toru Masaoka

The research and development of high density and low power DRAM and STT-MRAM with vertical body channel (BC-)MOSFET have been promoted to realize simultaneously high density integrations and high energy-savings.

We succeeded in operating Gbit level DRAM with peripheral circuit by vertical BC-MOSFET by low power supply for the first time in the world, and have been developed the integrated process technologies to realize high density and high speed cross point type STT-MRAM by vertical BC-MOSFET. Regarding application of vertical BC-MOSFET, we succeeded in widely reducing the layout area and standby power of SRAM in logic LSI, and have developed analog circuit of power supply and high efficient power circuit. Furthermore, as the application of AI and brain type LSI, nonvolatile neuron circuit and nonvolatile associative memory has brought about drastic effects on the low power consumption, high density and high speed. In addition, we’ve got great achievement in the control of interfacial atoms which can suppress Si missing phenomenon in order to scale down vertical BC-MOSFET in the future.

Under the industry-academia collaboration by The Center for Innovative Integrated Electronic Systems(CIES), we have created integrated circuit platform and innovative information processing base using vertical BC-MOSFET and have promoted and diversified the social spread of our technologies for the purpose of social implementation. We expect that our activities will contribute to coming information-oriented society, energy saving society and ubiquitous society.

The target of ACCEL project