CIESコンソーシアム

国家プロジェクト

JST ACCELプロジェクト

縦型BC-MOSFETによる三次元集積工学と応用展開

-

研究代表者

研究代表者

遠藤 哲郎 教授 -

プログラム

プログラム

マネージャー

政岡 徹 JST PM

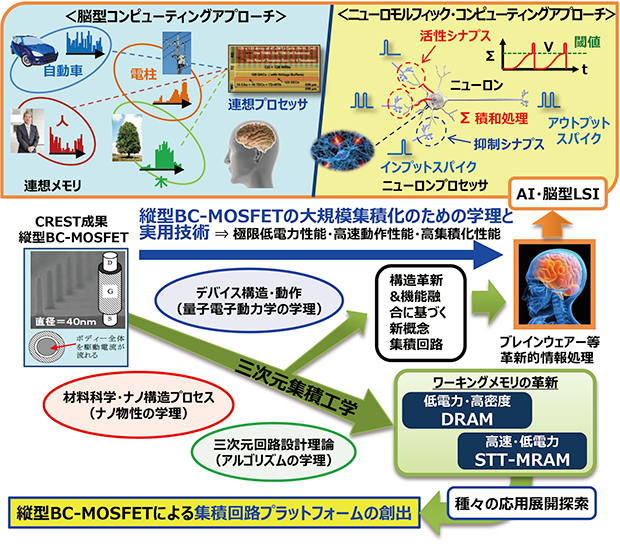

本プロジェクトでは、飛躍的な高集積化と省エネ性を同時に実現する縦型ボディーチャネル(BC-)MOSFETを基盤技術として、ワーキングメモリ(DRAM やSTT-MRAM)を中心にロジックLSI、アナログLSI、さらにはAI・脳型LSIなど様々な応用展開に繋がる共通基盤技術を開発してきました。

本研究開発により、縦型BC-MOSFETによる周辺回路を搭載したGbit級の大規模DRAMにて、低電源電圧の動作実証に世界で初めて成功するとともに、縦型BC-MOSFETによる高密度・高速クロスポイント型STT-MRAMの実現に向けた集積化プロセス技術を確立してきました。また、縦型BC-MOSFETの応用展開として、ロジックLSIにおけるSRAMの大幅な面積縮小と待機電力削減に成功し、電源系アナログ回路や高効率パワー回路なども開発してきました。さらには、不揮発性ニューロン回路、不揮発性連想メモリの研究開発により、AI・脳型LSIなどへの応用として、低消費電力・高密度・高速性において飛躍的な効果を挙げています。加えて、縦型BC-MOSFETの将来のスケーリングに向け、シリコンミッシング現象といった界面原子制御のための計算科学およびナノ計測からのアプローチに大きな成果も得られております。

以上、東北大学国際集積エレクトロニクス研究開発センター(CIES)を中核とした産学連携のもとに、縦型BC-MOSFETによる集積回路プラットフォームと革新的情報処理基盤を創出し、社会実装へ向けた本技術の社会普及の促進と多様化を進めてきました。これにより、来るべき情報化社会、省エネ社会、ユビキタス社会への貢献に期待されます。

本プロジェクトの目指す技術革新