CIES Consortium

CIES Joint ResearchProposal of Industry-Academic Collaboration

Integrated circuit implementation of recurrent neural networks for high-dimensional time-series data processing

Prof.

Takashi Morie

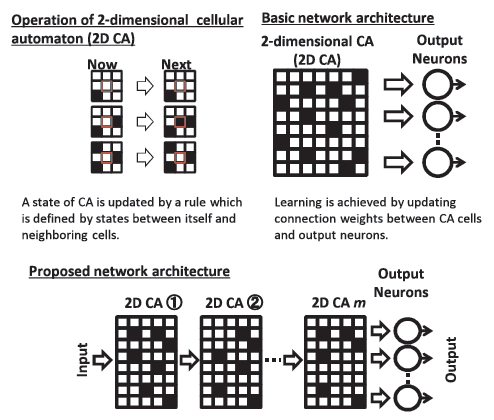

In recent years, a high-speed and low power custom LSI chip for high-dimensional data processing like images is necessary. In order to satisfy such necessary, information processing models are required, which are suitable to realize the LSI chip.

We are developing new-concept integrated circuits, which are designed based on the information processing models in which cellular automata (CA) having universal computation power and neural networks are combined. We aim to implement recurrent neural network circuits in which a single-layer CA operates as a multi-layer network in the time domain by changing cell-update rules at each time step. Our CA-based neural network architecture can perform high-dimensional data processing not only for static data but also for dynamic data by using spatiotemporal patterns generated in CA.

Host researcher: Prof. Tetsuo Endoh