CIES Consortium

National Projects

JST ACCEL Project

Three-dimensional integrated circuits technology based on vertical BC-MOSFET and its advanced application exploration

-

Prof.

Tetsuo Endoh -

Program Manager

Program Manager

Toru Masaoka

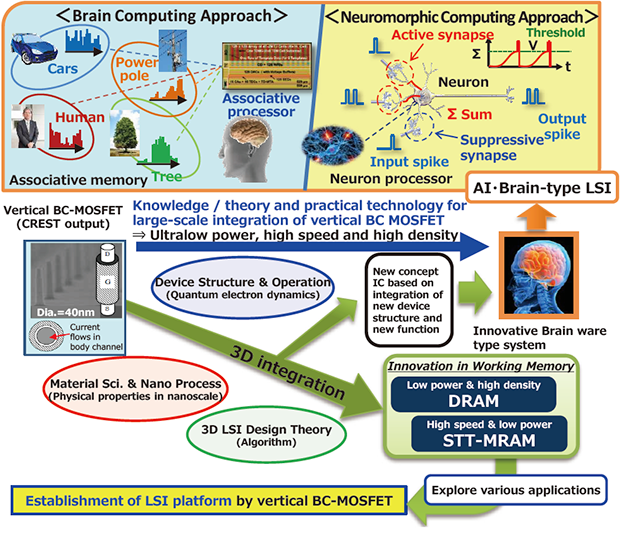

JST-ACCEL program “Three dimensional integrated circuits technology based on vertical BC-MOSFET and its advanced application exploration" (Research director: Prof. T. Endoh, Program manager: T. Masaoka) has started since April 2014, based on the accomplishments of JST-CREST program “Research and development of vertical body channel MOSFETs and its integration process” (Research director: Prof. T. Endoh). The research and development of high density and low power DRAM and STT-MRAM with vertical MOSFET have been promoted to realize simultaneously high density integrations and high energy-savings beneficial to logic LSI, analog LSI, AI, brain-type LSI, etc.

The target of ACCEL project