CIESコンソーシアム

産学共同研究

LSI(デバイス製造装置)

不揮発記憶ベース低消費電力・高性能VLSIプロセッサの自動設計環境の研究開発

-

羽生 貴弘 教授

羽生 貴弘 教授

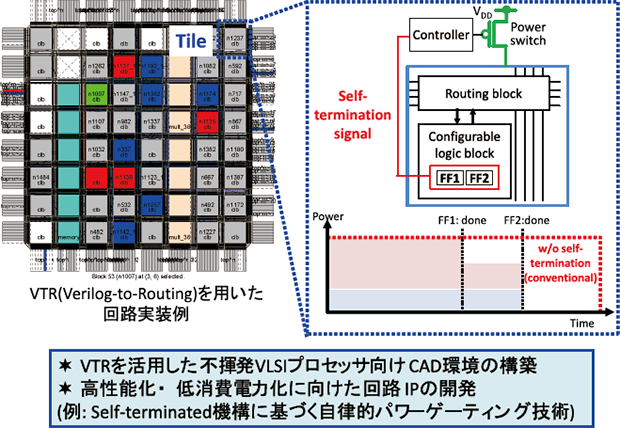

4x世代以降における深刻な待機電力に起因した性能限界を突破するため、不揮発ベース低消費電力・高性能IPの設計開発、それらを活用した自動設計環境を構築することが本テーマの課題です。その一環として、種々のアプリケーションに有用な不揮発FPGA(Field-Programmable Gate Array) に着目し、そのCAD環境構築を行っております。本研究では、オープンソースのFPGA CADツールVTR (Verilog-to-Routing) のライブラリに不揮発ベースIPを組み込むことでその基本フローを構築するとともに、高性能化・低消費電力化に向けた回路IPについても研究を行っております。本技術によりFPGAの電力効率が高まることで、モバイル機器やIoT機器などへの積極的応用が期待されます。

不揮発性FPGAの設計技術