CIESコンソーシアム

産学共同研究

LSI(デバイス製造装置)

不揮発性ワーキングメモリを目指したSTT-MRAMとその製造技術の研究開発

-

遠藤 哲郎 教授

遠藤 哲郎 教授

-

大野 英男 教授

大野 英男 教授

-

池田 正二 教授

池田 正二 教授

本研究テーマでは、スピントロニクス技術とシリコンCMOS技術の融合によるSTT-MRAMとその製造を、産学が連携して開発しています。これにより、飛躍的な省エネルギーシステムを実現する不揮発性ワーキングメモリの実用化を促進し、低炭素・省エネルギー社会の実現に貢献します。具体的には、以下の技術を一貫して開発しています。

- MTJ 材料・デバイス技術

CMOS集積回路と親和性の高いスピントロニクス素子である磁気トンネル接合(MTJ)素子の高性能化に向けた材料・デバイス・物理解析技術の開発。 - STT-MRAM の製造技術

STT-MRAM 製造のための300mmウェハを用いたユニットプロセス技術・プロセスインテグレーション技術の開発。 - 回路・設計・計測技術

スタンドアロンメモリや論理集積回路向け混載メモリとしてのSTT-MRAM の回路・設計・計測技術の開発。

CMOS集積プロセスと親和性を有する300mmウェハプロセスを用いたMTJの高熱処理耐性の要因究明

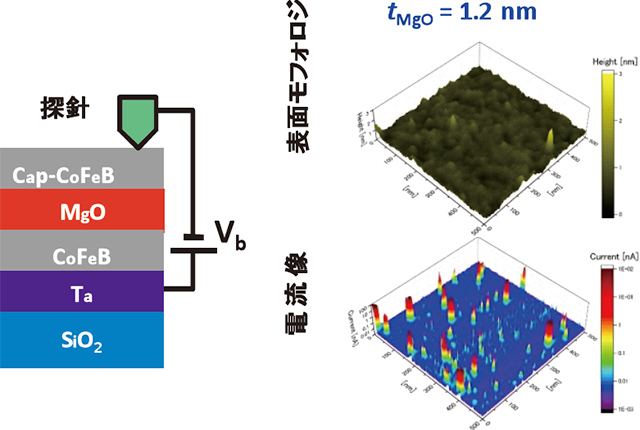

導電性AFMによるMTJ用MgOトンネル障壁膜のトンネル電流の評価

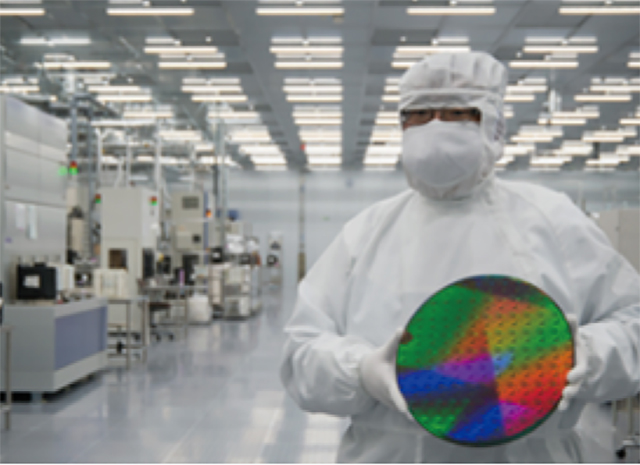

CIESにおける試作環境(最先端クリーンルームと300mmウェハ用製造設備) および300mm試作ウェハ

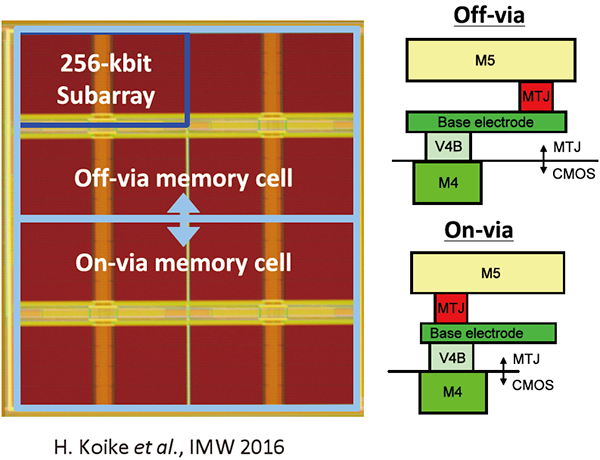

On-via STT-MRAM チップの開発