## 東北大学 国際集積エレクトロニクス研究開発センター

# Tohoku University Center for Innovative Integrated Electronic Systems

cie

# Open up Innovation

of integrated electronics from the international industry-a cademic alliance! Lead the recovery and new creation Leap toward world-class

First privately donated research and development center by founded Tohoku **University in Science Park**

## 300mm wafer process line, facilities for device, characterization & physical analysis in university campus for the first time in Japan

- \*1 Official support from Miyagi Prefecture through the system of special zones for the promotion of private investment (information service related industries) that was applied for jointly by the Miyagi prefectural government and municipal governments in the prefecture.

- \*2 Official support from Sendai City through an amount corresponding to the fixed property tax, etc., according to an agreement made by Tohoku University and Sendai City.

## **Our Mission** and Vision

The Center aims to contribute to the of next-generation integrated electronics systems, and work toward the creation of practical applications and new industries, through the research and development of innovative devices and its integrated electronic systems and constructing a consortium for this field under the international collaboration among industries, universities and government.

> feature Core technology

Integrated electronics is a technology that is used in all kinds of industrial products and social infrastructure, and determines the quality of our lives. To meet the social needs of carbon neutrality, AI/IoT/DX, and Society 5.0, innovative integrated electronics systems that can achieve significant low-power operation are required.

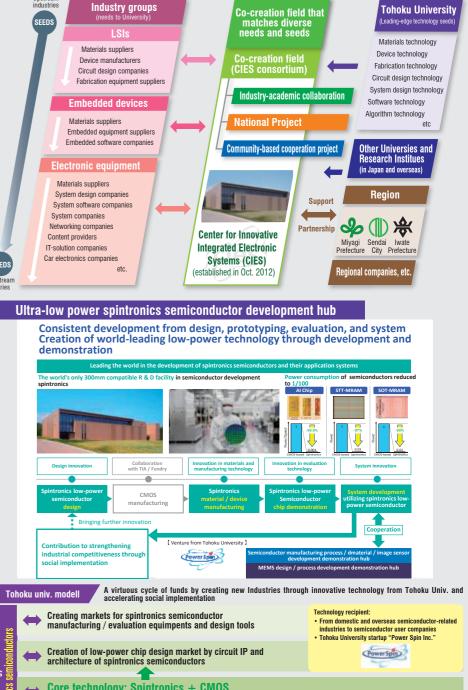

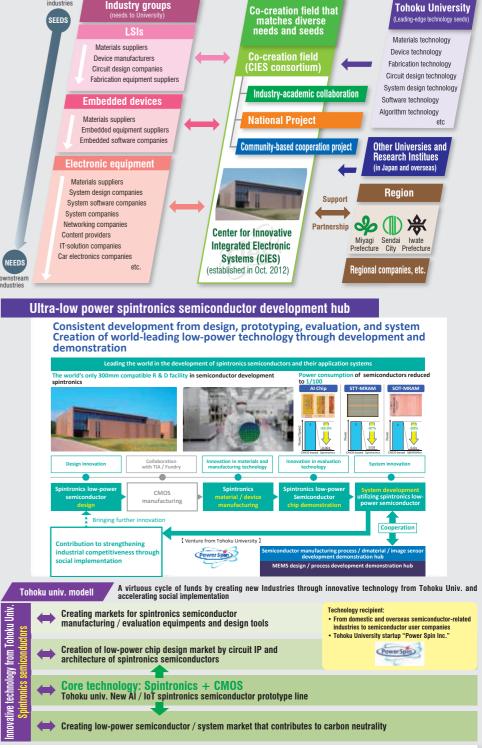

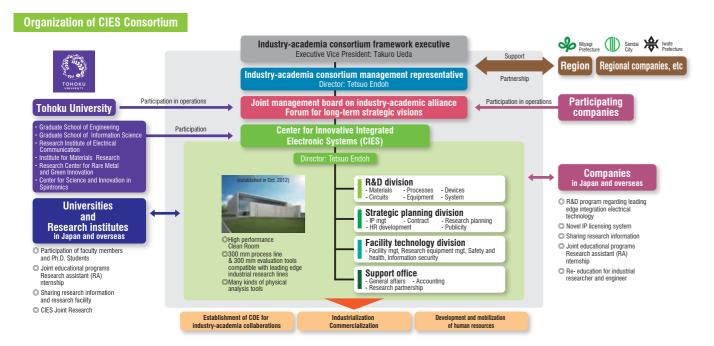

The Center for Innovative Integrated Electronic Systems (CIES) has conducted the CIES consortium consisting of industry-academia joint researches, major national projects, and regional collaboration projects through the cooperation of domestic and foreign companies from fields such as materials, equipment, devices, circuits and systems with support of local government. This center plays a part in the "Technology Co-creation for Semiconductor of Tohoku University" established by Tohoku University in 2021, and is expanding its R&D fields from spintronics to AI hardware and power electronics, and has promoted to develop core technologies related to integrated electronics. In addition, we are collaborating with Tohoku University startup "Power Spin Inc." to accelerate the social implementation of developed technologies and the further advancement of industry-academia collaboration

In June 2023, Japan's "Semiconductor/Digital Industrial Strategy" was revised, and "advanced technology development (spintronics technology) at academia-based centers" was positioned as a goal/strategy. We recognize that the responsibility of this center has increased significantly. At the G7 Hiroshima Summit, the "the U.S.-Japan University Partnership for Workforce Advancement and Research & Development in Semiconductors (UPWARDS) for the Future" was concluded. In response, this center is working on innovative semiconductor R&D, manufacturing, supply chain, and human resource development through collaboration between industry and Japanese and U.S. universities.

Through these activities, we hope to contribute to the development of our home prefecture, Miyagi Prefecture, the realization of a carbon-neutral society, and ensuring economic growth and economic security.

The development of this center to this day is due to the continued support and cooperation of many people. I would like to express my deepest gratitude to all for your dedication and continued support.

> March 2024 Tetsuo Endoh

> > Director of CIES

fe ature Sof tware

> Flexible joint research frame work between industry-academic alliance

Knowledge based on accomplishments between academic-industrial collaborations

Centralized administrative control and strategic operation of world-class intellectual properties of core technologies

Global standard joint research contracts

Advanced core technologies and intellectual properties from materials/devices/ processes to system/architectures, created and reserved at Tohoku University under its "Research First" principle and "Open Doors" philosophy, and "Practice-Oriented Research and Education" ethos.

etc.

- Materials technology

- Device technology

- Fabrication technology

- Circuit design technology

- System design technolo gy · Software technology

- Algorithm technology

CIES symbol and its messages

## Symbolic messages

Green-based color: Ecology & low power

Meaning of "i": Innovation & integration

### Three rings converging into " i ":

Integration of knowledge, science & technology with " i "

Collaboration of industry, academia and government with " i ",

Combination of many kinds of layer researcher from material to system with " i "

## **CIES Consortium R&D Scope**

- -

- H.H. H.

Technology Co-creation for Semiconductor of Tohoku University

## **R&D Division** (CIES Consortium)

ini,

| Α                        | Industry-Academic Collab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ooration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spintronics              | LSI<br>Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | STT/SOT-MRAM & -<br>Spintronics/CMOS Hybrid<br>processor -<br>R&D of technologies to automatically<br>and highly functional VLSI processors                                                                                                                                                                                                                                                                                                                                                                                    |

|                          | Embedded Device Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R&D of supersensitive magnetic sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                          | System<br>Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Research and development on embed<br>R&D of a VLSI platform for real-world                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3D<br>Nemory             | 3D Integrated Circuit Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R&D of 3D non-volatile memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Al Hardware <sub>N</sub> | Circuit<br>Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R&D of brain-type processing circuit t<br>R&D of error correction technologies<br>R&D of MTJ/CMOS Hybrid AI applicati                                                                                                                                                                                                                                                                                                                                                                                                          |

| Power Electronics        | Device/<br>Module/<br>Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R&D of WBG power module technolog<br>R&D of next-generation electrical com<br>R&D of integration and packaging tecl                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pow                      | Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R&D of next-generation high-power co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MOL<br>B                 | Technology<br>National Projects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R&D of next-generation high-power co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R&D of next-generation high-power co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                          | National Projects<br>MEXT Initiative to Establish Next-<br>generation Novel Integrated Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | National Projects     MEXT   Initiative to Establish Next-<br>generation Novel Integrated Circuits<br>Centers (X-NICS)     NEDO   Project for Research<br>and Development of Enhanced<br>Infrastructures for Post 5G<br>Information and Communications<br>Systems     NEDO   Development of Technology<br>for Designing Energy-Efficient Al                                                                                                                                                                                                                                                                                                   | Innovative spintronics X semiconducto<br>Development of advanced semiconduc<br>Photonics-electronic convergence inte<br>Feasibility study / Research and deve                                                                                                                                                                                                                                                                                                                                                                  |

|                          | National Projects     MEXT Initiative to Establish Next-<br>generation Novel Integrated Circuits<br>Centers (X-NICS)     NEDO Project for Research<br>and Development of Enhanced<br>Infrastructures for Post 5G<br>Information and Communications<br>Systems     NEDO Development of Technology                                                                                                                                                                                                                                                                                                                                              | Innovative spintronics X semiconductor<br>Development of advanced semiconduc<br>Photonics-electronic convergence inter<br>Feasibility study / Research and deve<br>at 1.5nm node and beyond<br>Development of design technology to a                                                                                                                                                                                                                                                                                           |

|                          | National Projects   MEXT Initiative to Establish Next-<br>generation Novel Integrated Circuits<br>Centers (X-NICS)   NEDO Project for Research<br>and Development of Enhanced<br>Infrastructures for Post 5G<br>Information and Communications<br>Systems   NEDO Development of Technology<br>for Designing Energy-Efficient Al<br>Semiconductor Chips and Systems   JAXA Space Exploration                                                                                                                                                                                                                                                   | Innovative spintronics X semiconductor<br>Development of advanced semiconductor<br>Photonics-electronic convergence inter<br>Feasibility study / Research and dever<br>at 1.5nm node and beyond<br>Development of design technology to a<br>Design efficiency of AI processing sem<br>Standby power-free system by MTJ/CI                                                                                                                                                                                                      |

|                          | National Projects   MEXT Initiative to Establish Next-generation Novel Integrated Circuits Centers (X-NICS)   NEDO Project for Research and Development of Enhanced Infrastructures for Post 5G Information and Communications Systems   NEDO Development of Technology for Designing Energy-Efficient Al Semiconductor Chips and Systems   JAXA Space Exploration Innovation Hub   JSPS                                                                                                                                                                                                                                                      | Innovative spintronics X semiconductor<br>Development of advanced semiconduc<br>Photonics-electronic convergence inter<br>Feasibility study / Research and deve<br>at 1.5nm node and beyond<br>Development of design technology to a<br>Design efficiency of Al processing sem<br>Standby power-free system by MTJ/Cl<br>(for space application)                                                                                                                                                                               |

|                          | National Projects   MEXT Initiative to Establish Next-<br>generation Novel Integrated Circuits<br>Centers (X-NICS)   NEDO Project for Research<br>and Development of Enhanced<br>Infrastructures for Post 5G<br>Information and Communications<br>Systems   NEDO Development of Technology<br>for Designing Energy-Efficient Al<br>Semiconductor Chips and Systems   JAXA Space Exploration<br>Innovation Hub   JSPS<br>Core-to-Core Program   MEXT Research and Development                                                                                                                                                                  | Innovative spintronics X semiconductor<br>Development of advanced semiconductor<br>Photonics-electronic convergence inter<br>Feasibility study / Research and deve<br>at 1.5nm node and beyond<br>Development of design technology to a<br>Design efficiency of Al processing sem<br>Standby power-free system by MTJ/Ct<br>(for space application)<br>Spintronics/Vertical elements of two-co                                                                                                                                 |

|                          | National Projects   MEXT Initiative to Establish Next-<br>generation Novel Integrated Circuits<br>Centers (X-NICS)   NEDO Project for Research<br>and Development of Enhanced<br>Infrastructures for Post 5G<br>Information and Communications<br>Systems   NEDO Development of Technology<br>for Designing Energy-Efficient Al<br>Semiconductor Chips and Systems   JAXA Space Exploration<br>Innovation Hub   JSPS<br>Core-to-Core Program   MEXT Research and Development<br>of Basic Technologies for Creating<br>Innovative Power Electronics   CAO<br>SIP Project (3rd Phase)                                                           | Innovative spintronics X semiconductor<br>Development of advanced semiconduc<br>Photonics-electronic convergence inter<br>Feasibility study / Research and dever<br>at 1.5nm node and beyond<br>Development of design technology to a<br>Design efficiency of Al processing sem<br>Standby power-free system by MTJ/CI<br>(for space application)<br>Spintronics/Vertical elements of two-d<br>Research and development of integrat                                                                                            |

| В                        | National Projects   MEXT Initiative to Establish Next-<br>generation Novel Integrated Circuits<br>Centers (X-NICS)   NEDO Project for Research<br>and Development of Enhanced<br>Infrastructures for Post 5G<br>Information and Communications<br>Systems   NEDO Development of Technology<br>for Designing Energy-Efficient AI<br>Semiconductor Chips and Systems   JAXA Space Exploration<br>Innovation Hub   JSPS<br>Core-to-Core Program   MEXT Research and Development<br>of Basic Technologies for Creating<br>Innovative Power Electronics   CAO<br>SIP Project (3rd Phase)   J-Innovation HUB (Integration<br>Community-based Cooped | Innovative spintronics X semiconductor<br>Development of advanced semiconduc<br>Photonics-electronic convergence inter<br>Feasibility study / Research and dever<br>at 1.5nm node and beyond<br>Development of design technology to a<br>Design efficiency of Al processing sem<br>Standby power-free system by MTJ/CI<br>(for space application)<br>Spintronics/Vertical elements of two-d<br>Research and development of integrat<br>Intelligent power electronics system wernational Development Ca                         |

| B                        | National Projects   MEXT Initiative to Establish Next-<br>generation Novel Integrated Circuits<br>Centers (X-NICS)   NEDO Project for Research<br>and Development of Enhanced<br>Infrastructures for Post 5G<br>Information and Communications<br>Systems   NEDO Development of Technology<br>for Designing Energy-Efficient AI<br>Semiconductor Chips and Systems   JAXA Space Exploration<br>Innovation Hub   JSPS<br>Core-to-Core Program   MEXT Research and Development<br>of Basic Technologies for Creating<br>Innovative Power Electronics   CAO<br>SIP Project (3rd Phase)   J-Innovation HUB (Integrated)                           | Innovative spintronics X semiconductor<br>Development of advanced semiconduc<br>Photonics-electronic convergence inter<br>Feasibility study / Research and development of design technology to a<br>Development of design technology to a<br>Design efficiency of Al processing sem<br>Standby power-free system by MTJ/Cf<br>(for space application)<br>Spintronics/Vertical elements of two-co<br>Research and development of integrat<br>Intelligent power electronics system wernational Development Ca                    |

| B                        | National Projects   MEXT Initiative to Establish Next-<br>generation Novel Integrated Circuits<br>Centers (X-NICS)   NEDO Project for Research<br>and Development of Enhanced<br>Infrastructures for Post 5G<br>Information and Communications<br>Systems   NEDO Development of Technology<br>for Designing Energy-Efficient AI<br>Semiconductor Chips and Systems   JAXA Space Exploration<br>Innovation Hub   JSPS<br>Core-to-Core Program   MEXT Research and Development<br>of Basic Technologies for Creating<br>Innovative Power Electronics   CAO<br>SIP Project (3rd Phase)   J-Innovation HUB (Integrated Electronics                | Innovative spintronics X semiconductor<br>Development of advanced semiconductor<br>Photonics-electronic convergence inter<br>Feasibility study / Research and dever<br>at 1.5nm node and beyond<br>Development of design technology to a<br>Design efficiency of Al processing sem<br>Standby power-free system by MTJ/Cf<br>(for space application)<br>Spintronics/Vertical elements of two-co<br>Research and development of integrate<br>Intelligent power electronics system wernational Development Ca<br>ration Projects |

Center for Innovative Integrated Electronic Systems

- R&D of material and device technologies

- R&D of manufacturing technologies

- R&D of measurement, evaluation and analysis technologies

- R&D of circuit and design tool technologies

- R&D of STT-MRAM·SOT-MRAM and Spintronics/CMOS Hybrid application processo

- esign environments for low-energy consumption based on non-volatile memory

- ors using ferromagnetic tunnel junctions

- lded security technology

- intelligent integrated systems

### chnologies

- in flexible information processing

- on processors

- onent technologies

- nologies

- verters for power and industry

### or research hub

- uctor manufacturing technology / terface memory module technolog

- opment of microfabrication core technologies for nonvolatile MRAM

- iccelerate industrial application of Al edge computing / iiconductors by CMOS/spintronics-hybrid technology and its applications

- MOS Hybrid technologies and its environmental tolerance test

- nensional materials

- ed power electronics for the realization of a decarbonized society

- ith USPM to support grid stabilization

- tegory)

- **Center for Innovative Integrated Electronic Systems**

- for IT

- for automotive

- nce of supply chains, and promotion of research and development

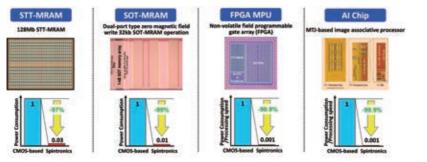

## R&D of STT/SOT-MRAM & Spintronics/CMOS Hybrid processor

In this R&D project, the technologies for STT/SOT-MRAM & Spintronics/CMOS Hybrid processor are Prof. Tetsuo Endoh researched and developed with combing the spintronics technology and the silicon CMOS technology, in joint efforts between industry and academia.

The actual R&D items are as follows. (1) Material/device technologies for the spintronics devices that have a compatibility for CMOS integrated circuits, 2Unit process/process integration technologies using the industry-standard 300mm Si wafers, 3Highly efficient measurement/evaluation technologies and multifunctional analysis technologies, ④Circuit and design tool technologies that cover from basic memory cells to large scale integrated circuits.

By integrating these developed technologies, we have designed STT/SOT-MRAM, and microcontrollers and AI application processors such as image recognition processors using spintronics/CMOS hybrid technology, and have demonstrated low power consumption performance in their integrated circuits prototyped using 300mm process lines. From now on, we will continue to promote further technological innovation through this project. In this way, we will accelerate the practical application of nonvolatile working memory and nonvolatile logic, which will realize dramatic low-power systems, and contribute to the realization of a carbon neutral society.

#### Industry – Academic Collaboration LSI Technology Α

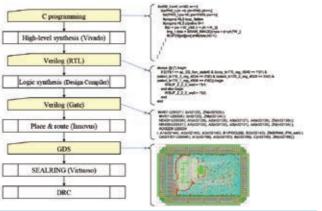

## R&D of technologies to automatically design environments for low-energy consumption and highly functional VLSI processors based on non-volatile memory

Prof. Takahiro Hanvu

To overcome a power-wall problem in 4x-nm CMOS era and beyond, our R&D project aims to develop nonvolatile (NV)-device-based logic-circuit Intellectual Properties (IPs) and its automatic design environment. The actual development items are as follows:

### 1. Development of a CAD environment for NV-FPGAs

FPGAs (Field-Programmable Gate Array) is a attractive hardware platform for various applications. We have been establishing the environment by combining an open-source CAD tool, called Verilog-to-Routing (VTR), with nonvolatile logic-circuit IPs.

2. Development of a NV-based circuit IPs

We have also been developing logic circuit IPs for realizing a further energy-efficient/highly functional NV-FPGA

3. Applications to Al accelerators

As an effective application, we have been developing NV-FPGA-based energy-efficient AI accelerator.

It is expected that the NV-FPGA is utilized in a wide variety of applications such as IoT and mobile devices

Figure: Example of an automatic circuit-design CAD environment based on high-level synthesis (C language). Utilizing C-language-based design assets, it is possible to design nonvolatile logic circuits/VLSI processors. As a result, it could become easy to explore the optimal design architectur

#### Industry – Academic Collaboration Spintronics Embedded Device Technology Α

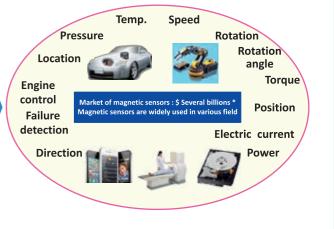

## R&D of supersensitive magnetic sensors using ferromagnetic tunnel junctions

Magnetic sensors are widely used in various fields, such as environment, security, medical appliances, information technology, automobiles, etc. Additionally, the market scale of magnetic sensors is several billion dollars\*. In this research, we will develop magnetic sensor devices with high sensitivity, small size, low power consumption and low cost using magnetic tunnel junctions (MTJs). A revolution in market of magnetic sensors is expected by realization of high-performance MTJs.

\* IHS iSuppli Market Research

| Nano magnet<br>Insulator | Advantages of our sensor<br>✓ High sensitivity<br>✓ Small size<br>✓ Low power consumption |  |

|--------------------------|-------------------------------------------------------------------------------------------|--|

| Nano magnet              | Low price                                                                                 |  |

#### Industry – Academic Collaboration Spintronics System Technology Α

## Research and development on embedded security technology

This R&D project aims to study emerging security technologies for IoT (Internet of Things) where numerous and various devices are connected to network. In particular, we study device security and remote authentication technologies for M2M (machine-to-machine) communication. The study for device security includes implementation technologies of confidential communication and authentication under limited resource and power supply. In contrast, the study for remote authentication includes efficient entity authentication technologies between terminal(s) and server(s)/terminal(s). By the above studies, we expect to establish fundamental technologies for connecting various devices in a safe manner to the cyber space.

<sup>Prot.</sup> Takafumi Aoki

Naofumi Homma

Implementation security evaluation for M2M devices

Prototype application of remote authentication between terminal

R&D of a VLSI platform for real-world intelligent integrated systems

The aim of our project is to develop a new reconfigurable LSI with low power, high performance and high soft-error tolerance for real-world intelligent systems, big-data applications and infrastructure applications. For state-of-art process technologies with smaller feature sizes, 3-D integration and an ultra low supply voltage, we develop synchronous/asynchronous hybrid circuits with autonomous supply-voltage control, MRAM-based nonvolatile logic circuits for low stand-by leakage power and high soft-error tolerance, and high-level design tools that allow us to exploit easily reconfigurable LSI applications using these advanced circuit technologies.

> Computer architecture by ultra-low-power reconfigurable LSI (FPGA) based on non-volatile logic with fine-grain power-control capability

# Industry – Academic Collaboration Al Hardware Circuit Technology

## R&D of brain-type processing circuit technologies

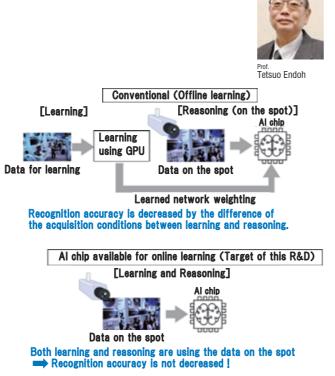

In this research and development, we have developed edge Al processors with low power consumption and high speed which are important for Societv5.0.

In the conventional edge AI processors, after learning process which has been performed offline using GPU, learned parameter data have been used for inference process of AI chip. Generally, since the data acquisition conditions at inference (on the spot) are different with those at learning, the recognition accuracy of AI chip is always decreased.

In order to solve this problem, we have researched and developed the architecture / circuit / device technologies of the high-accuracy and ultra-high-speed edge AI processors which can learn and make an inference on the spot. MRAM attracts attention as nonvolatile memory, so we establish a base in the architectures / circuits to utilize MRAM thoroughly, and continue to develop the system-level fine-grain power gating, the high efficiency data transfer mechanism to dissolve data transfer bottleneck, the circuits / devices of MRAM suitable for uses, and the novel AI processor architectures with offline/online learning.

Asynchronous architecture with non-volatile logic

PE

Handshake communication

adaptive power contro

no dynamic powe

in inactive sta

Data

PE

Non-volatile logic circuit

**Nonvolatile FPGA**

## Industry – Academic Collaboration Al Hardware Circuit Technology

## R&D of error correction technologies in flexible information processing

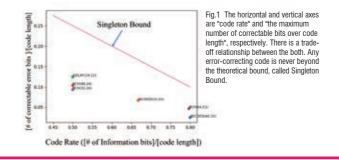

In DRAMs and other storage devices, cosmic rays, temperature conditions, and other factors can cause the storage bits to flip, resulting in incorrect calculation results. ECC (Error Correction Code) technology has been developed to detect and correct these errors, by converting the original data into an error correction code with redundancy, which can detect errors and restore the original data. However, in order to increase the correction capability (i.e., to detect and correct more errors), a large amount of redundancy is required to match the capability (Fig. 1).

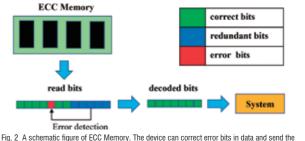

ECC technology is also used in "memory", an important component in computers, and in particular, memory that has an ECC circuit implemented as hardware is called ECC memory (Fig.2). Normally, the ECC algorithm called "SECDED", which is capable of correcting 1-bit errors and detecting 2-bit errors, has been commonly used in ECC memory. In this study, we have been exploring and verifying not only SECDED, but also the most suitable ECC algorithm with high correction capability for STT-MRAM based on software, which is easy to implement and improve by trial and error. The BCH code can select the number of bits that can be corrected under certain constraints. On the other hand, Golay codes can detect and correct errors and recover data with a simpler calculation than BCH codes, although the code length and the number of correctable bits are fixed.

## A Industry – Academic Collaboration Al Hardware Circuit Technology R&D of MTJ/CMOS Hybrid Al application processors

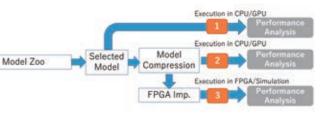

Advances in deep learning (DL) technology and parallel processors (e.g., GPUs) that can perform large-scale operations at high speed have made it possible to achieve highly accurate and fast object recognition, which was difficult until now (Figure 1). However, while these processors are capable of high-speed computation, they also consume a lot of power for accessing storage circuits, so it is necessary to reduce power consumption when installing them in in-vehicle computers and edge devices. Power consumption reduction can be expected by compressing and optimizing the DL algorithm. Furthermore, by applying power gating (PG), which takes advantage of the non-volatility of MTJ/CMOS hybrid circuits, power consumption reduction can be expected from power reduction during memory circuit access

Therefore, we are developing a scheme to analyze the performance (recognition accuracy, speed, and memory access patterns) for DL algorithms running on various hardware (Figure 2). By analyzing memory patterns and improving algorithms suitable for PG, we aim to develop DL algorithms that match MTJ/CMOS hybrid circuit technology.

results recognized by one of famous algorithms, YOLOv3 The algorithm can detect small objects in the

> Fig. 2 A scheme of performance analysis of DL model selected from Model Zoo, being executed on CPU/GPU/ FGA. The analysis includes detection accuracy, speed and memory performance analysis, though which we try to select suitable DL models, and modify algorithm of those as well.

right data to the system, thanks to redundant bits included within the data.

## Research and Development of WBG Power Module Technology

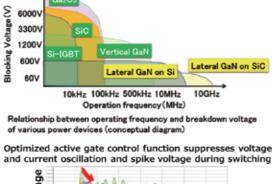

In this research theme, industry-academia collaboration is underway to develop power module technology that maximizes the features of wide bandgap (WBG) power devices such as SiC-MOSFETs and GaN on Si lateral power devices, which combine low loss and high speed. This will contribute to the realization of high-performance electric vehicles (EVs), compact and high-efficiency power supplies for data centers, and smart cities that optimize power supply operations.

Following technologies are being developed. 1. Voltage and current oscillation suppression technology for WBG power modules

Development of low-inductance module technology to suppress voltage and current oscillation and spike voltage during switching while taking advantage of the high-speed performance of WBG power devices.

- Development of active gate drive circuit technology.

- 2. low thermal resistance technology

- Development of high thermal conductivity insulating substrate technology to suppress temperature rise during high frequency operation of WBG power chips, which are becoming smaller and higher power density.

- 3. high heat dissipation technology

Development of new air-cooled and water-cooled cooler technologies to cope with the increasing capacity of WBG power devices.

## A Industry – Academic Collaboration **Power Electronics** Equipment Technology

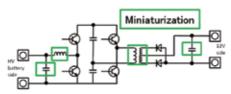

## Research and development of next-generation electrical equipment technology

This contributes to the realization of a highly efficient and ultracompact DC-DC converter that can handle the increased power supply due to the increase in the number of sensors and actuators associated with the progress of automated driving in automobiles.

- We are developing the following technologies.

- 1. High-frequency drive technology for DC-DC converters Development of high-frequency drive technology using ultra-highspeed GaN on Si lateral power devices that enables downsizing of

passive components such as passive components such as isolation transformers, reactors, and capacitors in DC-DC converter.

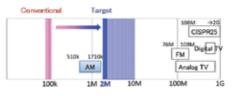

2. Low noise technology

Reduction of noise filter (miniaturization of DC-DC converter) by driving DC-DC converter at high frequency (2MHz or higher) above AM radio frequency band, and development of optimum driving technology to suppress ringing noise.

3. High power technology

Development of parallel connection operation technology and multiphase operation technology for GaN on Si devices

Miniaturization of passive device by high frequency

DCDC converter circuit

## Reduction of AM radio noise filter by 2MHz drive

DCDC converter operating frequency for commercial frequency band

#### Industry – Academic Collaboration **Power Electronics** integration Technology Α

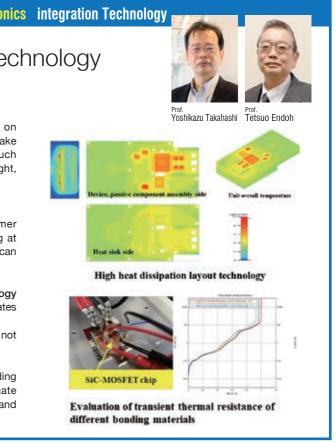

## R & D on assembly integration technology

In this research theme, industry and academia collaborate on research and development of assembly integration technologies to take advantage of the superior characteristics of new WBG devices such as GaN-on-Si and SiC. This contributes to reducing the size, weight, functionality, and performance of power electronics equipment.

- We are developing the following technologies.

- 1. Passive component technology

Development of low loss / ultra-small reactor and transformer technology with low iron loss and copper loss even when driving at high frequencies, and development of capacitor technology that can withstand high temperatures of 250 degrees or higher.

2. Power integrity technology

and high heat dissipation layout technology Development of power integrity technology for various PCB substrates applied to high integration density power electronics circuits. Development of high heat dissipation layout technology that does not increase chip temperature at high frequency

3. Bonding materials and technology

Development of low thermal resistance and high reliability bonding materials and technology for assembling GaN on Si devices, gate circuits, and various passive components on insulating substrates and cooling structures.

## A Industry – Academic Collaboration Power Electronics Circuit Technology

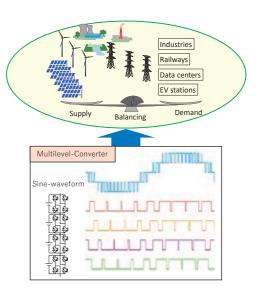

## R&D of next-generation high-power converters for power and industry

In this R & D, with a view to contributing to the mass introduction of renewable energy and electrification, we are developing circuits and control technologies for high-power converters. The converters are for 1) PCSs for wind power generation and solar power generation, etc. 2) The various power equipment installed in factories, large construction

machines, ships and EVs etc.

Power converters can be increased in output power by connecting multiple small converters cascaded in series using multi-level technology. Such multi-level converters can output sine-wave voltages with low.

Specifically, the following technologies has been being developed. (i) Circuit and control technologies to significantly reduce the size and loss

- of multi-level converters

- (ii) Circuit and control technologies to improve the robustness of multilevel converters

enter for Innovative ntegrated Electronic S

## B National Project MEXT Initiative to Establish Next-generation Novel Integrated Circuits Centers (X-NICS)

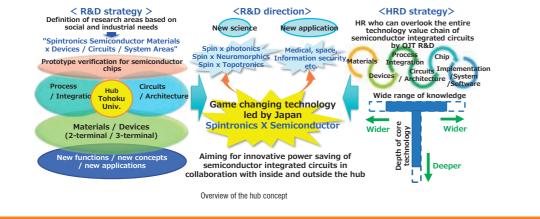

Innovative spintronics X semiconductor research hub

We will put spintronics, which is a game change technology for low-power integrated circuits led by Japan, at the core. We will comprehensively conduct from R&D of new materials and devices, R&D of circuits, architectures and integrated technologies that bring out their characteristics, to prototype verification for low-power semiconductor chips that accelerate the development of CMOS semiconductors with collaborative and cooperating organizations. While promoting this activity, we will lead the creation of new science and the transformation of the information society by cultivating the fusion area of electronics with light / neuro / topology, and pioneering new applications such as medical care, space, and information security, and then contribute to the improvement of our research and development capabilities related to semiconductors. We have young researchers and students actively and strategically participate in this hub, and develop human resources who have the practical ability and a bird's-eye view.

Project for Research and Development of Enhanced Infrastructures for Post 5G Information and Communications Systems B National Project NEDO

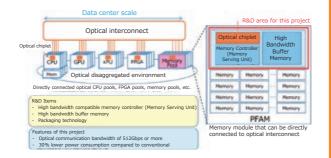

Development of advanced semiconductor manufacturing technology Photonics-electronic convergence interface memory module technology

Tohoku University will participate in a project as a subcontractor after the "Photonics-electronic convergence interface memory module technology" jointly proposed by Kioxia Corporation and NTT was adopted in NEDO Project for Research and Development of Enhanced Infrastructures for Post 5G Information and Communications Systems.

In the IOWN initiative promoted by NTT, data centers require disaggregated computing, which connects multiple computing resources (such as CPUs and GPUs) directly to optical interconnects in order to efficiently process a wide variety of realtime requests from multiple users. Additionally, memory must be shared by multiple computing resources to improve usage efficiency.

In this technology development, Tohoku University has subcontracted part of the technology development of photonic fabric attached memory module (PFAM), which realizes memory that can be accessed by broadband optical access from multiple computing resources via optical interconnect.

#### National Project B NEDO

## Feasibility study /

## Research and development of microfabrication core technologies for nonvolatile MRAM at 1.5nm node and beyond

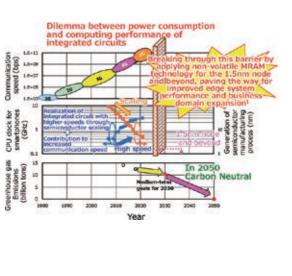

In order to achieve low latency in the post-5G era for edge-side systems such as smartphones and IoT/AI processors, high performance edge computing is necessary under the power supply limitation environment. However, the dilemma of power consumption and computing performance will continue to be an issue in the development of technologies beyond the 1.5nm node, which is an extension of conventional silicon technologies. As a result, there will be limitations in advancing the performance of edge systems and expanding their business fields.

In this theme, research and development of microfabrication technology for nonvolatile MRAM at the 1.5nm node and beyond will contribute to overcoming the dilemma between power consumption and computing performance by reducing power consumption through nonvolatility and miniaturization based on MRAM/CMOS hybrid LSI technology. This will enable the realization of edge-side systems with low power consumption and low latency for the post-5G era, and contribute to carbon neutrality as a synergistic effect of its social implementation.

Based on the following, we are developing fundamental microfabrication technologies for nonvolatile MRAM for the semiconductor process 1.5nm node and beyond:

Tokyo Electron Limited (TEL): Development of core technology for RIE etching at MTJ pitch for the 1.5nm node and beyond

Tohoku University, CIES: Processes development, fabrication, and evaluation to verify the developed RIE technology

#### Development of technology for designing energy-efficient AI semiconductor chips and systems National Project B NEDO

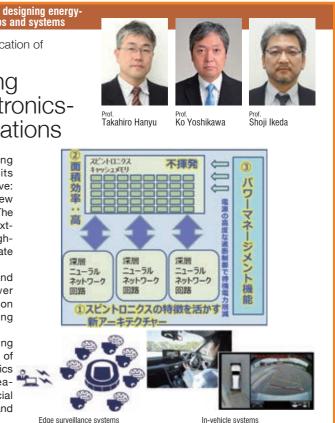

Development of design technology to accelerate industrial application of Al edge computing

## Design efficiency of AI processing semiconductors by CMOS/spintronicshybrid technology and its applications

The research project on "Design efficiency of AI processing semiconductors by CMOS/spintronics-hybrid technology and its applications (principal investigator: Tohoku University; representative: prof. Takahiro Hanyu)" proposed in 2022 was accepted by the new energy and industrial technology development organization (NEDO). The project was adopted by NEDO for "development of AI chips and nextgeneration computing technology enabling high-efficiency and highspeed processing / development of design technology to accelerate industrial application of AI edge computing"

The current AI processing handles a large amount of data and requires high-speed computation, which results in huge power consumption. In particular, since the allowable power consumption is limited at the edge, innovative and power-efficient AI computing technologies are desired.

This research aims to develop a high power-efficient computing technology suitable for edge AI that maximizes the characteristics of CMOS technology, which is currently the mainstream, and spintronics technology, which is highly compatible, non-volatile, and areaefficient, by integrating these technologies. In addition, as its social implementation, we will apply the technology to in-vehicle systems and to next-generation surveillance systems such as watchdog systems.

enter for Innovativ tegrated Electronic S

Project for Research and Development of Enhanced Infrastructures for Post 5G Information and Communications Systems

Takashi Havakawa

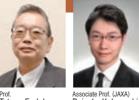

## Standby power-free system by MTJ/CMOS hybrid technologies and its environmental tolerance test (for space application)

A research proposal "Standby-power-free system by MTJ/CMOS hybrid technology and its environmental resistance test (for space applications)" by CIES, Tohoku University in FY2019 was selected for the request for proposal (RFP) by the JAXA Space Exploration innovation Hub to expand "the human sphere of life and active area by exploring the solar system frontier". The project was selected as a follow-up research in FY2021, and is accelerating research and development.

For space exploration beyond Moon and Mars, long-term missions of more than 10 years are expected in environments where solar energy is weak, so ultra-low power electronic systems that cannot be achieved with existing technologies is required. Another important issue for spacecraft electronic systems is the need for both standby power and space radiation resistance.

In this proposal, we will research a system that does not require standby power using MTJ/CMOS hybrid technology that integrates CMOS technology and MTJ, which is a spintronic device developed by us. We aim to realize innovative semiconductor devices and integrated circuits that improve efficiency and reduce power consumption by orders of magnitude. Specifically we will conducted the research on the materials for higher performance and higher reliability, and the MTJ/CMOS hybrid devices/circuits/integration process/chip technologies.

Based on the reliability evaluation including radiation tolerance test by JAXA, we aim to create a power-free integrated circuit that has environmental tolerance in addition to the non-volatility and high speed in MTJ/CMOS hybrid chips. This contributes to the solution of the research theme "Research on Standby Powerless Systems" specified by JAXA.

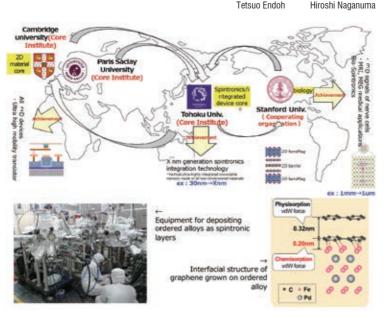

#### B National Project Core to core project

Research Center Formation Project - A. Advanced Center Formation Type -"Spintronics/Vertical elements of two-dimensional materials"

Prof. Tetsuo Endoh

This research theme proposing a new vertical device by integrating current spintronics technology with two-dimensional materials in order to create next-generation spintronics technology. The aim is to integrate distinctive research from Japan, the UK, France, and the US.

1. Japan-UK collaboration

The University of Cambridge in the UK has worldclass film production technology and theoretical analysis for two-dimensional materials.

2. Japan-France cooperation

France's CNRS/Thales has been established spintronics basic theory, led by Dr. A. Fert, who won the Nobel Prize in Physics in 2007. In this research, we will contribute to the creation of new spintronic devices using advanced microfabrication facility for two-dimensional materials.

3. Japan-US cooperation

Japanese team collaborate with Stanford University on biosensing research field as a new application possibility for spintronics devices.

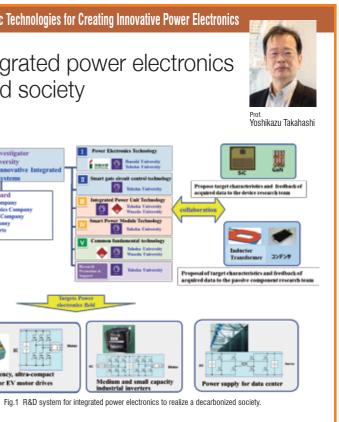

#### National Project MEXT Research and Development of Basic Technologies for Creating Innovative Power Electronics B

## Research and development of integrated power electronics for the realization of a decarbonized society

This research theme aims to research and develop circuit systems that take full advantage of the superior performance of WBG devices to the limit, and to realize smaller size, higher performance, higher power density, and higher efficiency in next-generation inverters and power supplies through the development of ultra-compact, high-performance power modules, power unit and the application of optimal passive components

Applied products include motor drive inverters for EVs small and medium-sized inverters for industrial use, and power supplies for data centers, which are widely used in society to handle small and medium power ranges

Tohoku University, which is the representative institution, Ibaraki University and Waseda University, which are research-sharing institutions, and an advisory board as a cooperating company will promote research and development on five subthemes that are important for power electronics research.

By advancing these research and development efforts, we will create next-generation power electronics technologies and products that will lead the world and contribute to the realization of a decarbonized society.

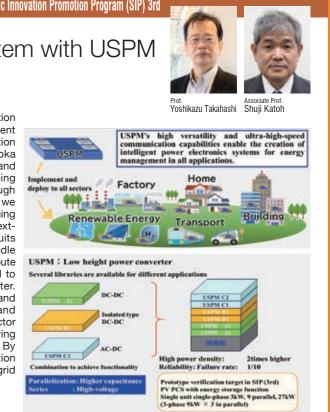

**B** National Project Cabinet Office Cross-ministerial Strategic Innovation Promotion Program (SIP) 3rd

## Intelligent power electronics system with USPM to support grid stabilization

This R&D aims to develop elemental technologies for next-generation high power density USPMs with a wide range of energy management (EMS) applications and grid stabilization functions, as well as application technologies for smart inverters and smart power supplies. Nagaoka University of Technology is the lead organization for this research and development, and Tohoku University CIES is in charge of developing reliability-enhancing technologies for next-generation USPMs through optimal packaging technology as a joint research institute. Specifically, we are working to suppress jump voltage and reduce noise during switching by reducing the inductance of power device packages applied to nextgeneration USPMs, and to achieve high integration with gate circuits and passive components in pursuit of a compact and easy-to-handle structure. In addition, in order for the next-generation USPM to contribute to the stabilization of the power system, it is necessary to respond to synchronization and pseudo-inertia forces as a grid-forming inverter. We will conduct research and development on package structures and gate drive methods that enable suppression of heat generation and temperature rise and overvoltage suppression of power semiconductor chips during high-current operation, which are essential for improving the synchronization and pseudo-inertia of next-generation USPMs. By advancing these R&D activities, we will contribute to the construction of intelligent power electronics systems with USPMs that support grid stabilization

enter for Innovative tegrated Electronic S

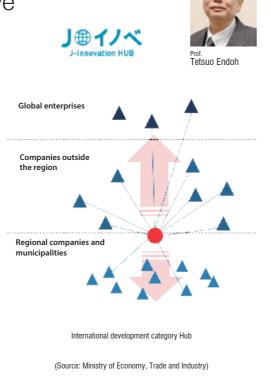

#### C J-Innovation HUB (International Development Category)

## Activities for J-Innovation HUB initiative (International development category)

CIES was selected as the 1st industry-academia base of the "J-Innovation HUB Initiative", a project of the Ministry of Economy, Trade and Industry (METI) launched in 2020 (International development category).

Under this initiative, METI targets regional innovation hubs (mainly universities), and assesses and selects outstanding industryacademia bases that are playing a leading role as hubs for networks of companies. The aim is to enhance their creditworthiness, focus public support measures on them, and enhance the capabilities of the topranking hubs. METI selects the hubs in two categories: the international development category and the regional contribution category.

METI will advance dialogues with each of the selected hubs and will provide them with tailor-made support measures, including budgets and relaxation of regulations

Partners participating in the activities of CIES are expected to take advantage of the preferential treatment of this J-Innovation HUB policy.

#### Community-based Cooperation Project Integrated Electronics Car Electronics D

## Promotion of regional cooperation in integrated electronics and car electronics fields

This activity aims to spread excellent core technologies of local companies to the world with cooperation of local government and administrative agencies. In particular, the following activities have been promoted.

- 1) Sophisticate core technologies of local companies by integrating fundamental technologies and scientific knowledge of CIES;

- 2) Develop cooperation among local companies in electronics and automotive field, and apply the core technologies to new application, and work on study meeting of commercialization in cooperation with Miyagi and Iwate Prefectural Government;

- 3) Promote cooperation between local companies and world-class companies at CIES as a place to meet, and spread the core technologies of local companies to the world.

Under these activities, unique core technologies by local companies will be applied to integrated electronics and car electronics, and the application and commercialization of the innovative devices will be promoted to next generation of IT and car electronics.

CIES will continue to contribute to Tohoku promotion.

CIES **Technology Matching** Meeting ~a place to meet~ Miyagi Advanced Electron And Machinery Industry Miyagi Automotive Industr Promotion Council <Seeds of Local Companies> ds of CIES> <Needs of local Companies> Few chance of finding customer eds of CIES> possessing technologies High barriers to enter new hnologies ufficient resource for scientific derstanding

Tetsuo Endol

Basic policy of the Community-based cooperation

## The Semiconductor Technology Co-creation Center

## Toward Japan's largest semiconductor R&D ecosystem

### O Background and purpose

In order to contribute to strengthening the international competitiveness of Japan's semiconductor industry, the Tohoku University Semiconductor Technology Co-Create center will leverage its openness as a university to share the university's diverse results with various institutions, creating synergies and building an R&D ecosystem.

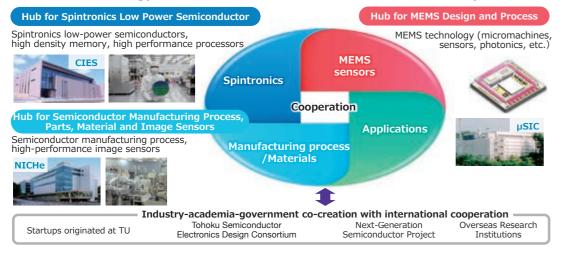

### O Initiative details and effects

This co-creation organization has three hubs, and we, center for innovation integrated Electronics systems is one of them, as a "Hub for Spintronics Low Power Semiconductor". We are responsible for the design, prototype demonstration, and evaluation of next-generation memory MRAM, as well as its system development. In addition, Tohoku University has the "Hub for Semiconductor Manufacturing Process, Parts, Material and Image Sensors" based on ultra-clean process technology and image sensor technology and the "Hub for MEMS Design and Process," which is responsible for R&D, technical evaluation, and prototyping of various devices and advanced packaging technologies. We collaborates with these two centers to lead semiconductor research in Japan.

https://semicon.tohoku.ac.jp/en/

## MEXT Initiative to Establish Next-generation Novel Integrated Circuits Centers (X-NICS)

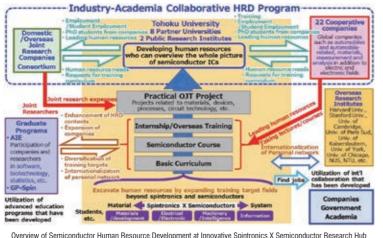

MEXT Initiative to Establish Next-generation Novel Integrated Circuits Centers (X-NICS) Semiconductor Human Resource Development at Innovative Spintronics X Semiconductor Research Hub

### X-nics industry-academia collaboration seminar in 2023

We aim to develop human resources who have a bird's-eye view of the technology value chain of semiconductor integrated circuits, from materials, elements, design, circuits, architecture, integration technology, prototyping, evaluation, and systemization while deepening our own core technologies and specialized fields. We also aim to develop human resources with business sense and planning ability by utilizing practical education provided by partner companies. Furthermore, in addition to educating students, we are also working on recurrent human resource development of young teachers and engineers

| Technology and IP for automotive semiconductors, etc.                  | Sumitomo Electric Industries |

|------------------------------------------------------------------------|------------------------------|

| Electrical industry and its IP strategy                                | Panasonic                    |

| Future created by semiconductors                                       | JEITA                        |

| Towards transformation into mobility company                           | Toyota Motor                 |

| Changes in car society and challenges for automotive semiconductors    | DENSO                        |

| Beauty of NAND                                                         | Western Digital              |

| Computing platform that accelerates Al                                 | NEC                          |

| Beyond 5G technology                                                   | NICT                         |

| Forefront of flash memory                                              | KIOXIA                       |

| SoC and OS transition and outlook for IVI                              | AISIN                        |

| Power semiconductor module packaging technology that contributes to CN | FUJI ELECTRIC                |

| Technology trends in advanced packaging                                | Resonac                      |

| Computing & Memory                                                     | Intel                        |

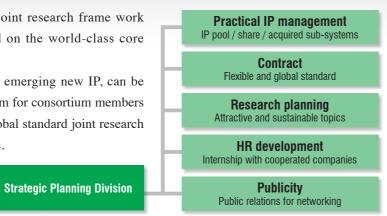

**Strategic Planning Division**

Strategic planning division establishes flexible joint research frame work in order to operate it efficiently and actively, based on the world-class core technologies and experienced administration support.

Intellectual Property (IP), which are core IP and emerging new IP, can be managed as our valuable asset and enable to provide them for consortium members efficiently. Based on this new IP system, flexible and global standard joint research contracts are ready for domestic and overseas companies.

## **Advanced Human Resource Development Program**

The following programs have been implemented with the objective of developing young research resources in the field of integrated electronics technology.

### ① Lectures and curriculum delivered by industry-academia ioint faculties (credit courses)

In these courses, we explain the types of talents required in industry sectors and society as a whole, create curriculum based on those principles, and offer lectures by members of industry-academia joint faculties.

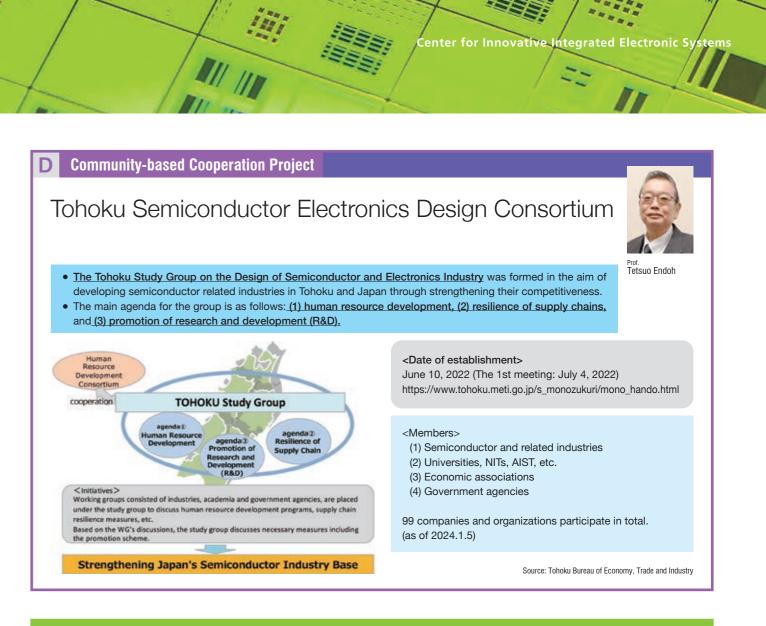

### (2) Participating in Tohoku Semiconductor Electronics Design Consortium

We participate in Tohoku Semiconductor Electronics Design Consortium responsible for the human resource development etc. in Tohoku established by Ministry of Economy, Trade and Industry

### (3) Industry-academia collaboration OJT system promoting advanced human resource development RA system within the CIES consortium

We elucidate the responsibilities of people engaged in industryacademia collaborative research and aim to encourage graduate sudents /postdoctoral / young researchers to participate in industry-academia collaborative research by providing compensation.

X-nics RA Students

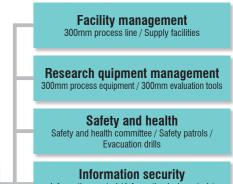

## **Facility Technology Division**

Facility technology division focuses on four main functions in order to achieve safety, stable, and efficient research and development. Not only gas and liquid leakage, particle sensor management, in/out security control for research zone, but also 24 hours monitoring of electricity, gas and water can provide safe and validity research and development circumstance.

We operate a clean room with a 300mm wafer process line. Management duties include daily inspections to ensure stable and safe operations. Maintenance is carried out to ensure stable operation of the 300mm wafer process equipment installed in the clean room.

As for ensuring safety, safety education is conducted to the facility and equipment users. To provide instruction and improve safety and health, we established a safety and health committee, safety patrols, and evacuation drills. As for information security, we manage network security for information

equipment in CIES and also provide education to facility and equipment users.

**Facility Technology Division**

enter for Innovative ntegrated Electronic S

### RA System within X-nics

Human resources with business sense and an overview of the entire technological value chain of semiconductor integrated circuits, including materials, devices, design, circuits, architecture, integration technology, prototyping, evaluation, and systemization, who can also deepen their own understanding of core technologies and specialized fields.

#### Internship system

A promotion system has been organized targeting doctoral course students (DCs), post-doctoral fellows (PDs), and young faculties etc., to help to take part in internships at companies participating in CIES consortium

### **(4)** Participating in University program Center for Science and Innovation in Spintronics (CSIS)

In the certification of "Designated National University", the CSIS is aiming to establish a hub that pioneers new field of "Spin-Centered Science" in the world by strategically gathering outstanding researchers through international collaborations.

#### Center for Spintronics Research Network, Tohoku University (CSRN)

The CSRN is aiming at the formation of research network hub to promote collaborative research with domestic and international institutes for accelerating international competitiveness of world-leading spintronics research, creating new industries, strengthening the current industry and developing next generation human resources.

#### Graduate Program in Spintronics, Tohoku University (GP-Spin)

This program aims to foster researchers who can play an active role internationally in spintronics area which is our strength research field This program is supervised by world leading professors including CIES members

### Tohoku Forum for Creativity

We participate in a university program that develop human resources who can start a business or play an active role in a company through the research. The program cultivates not only fundamental business skills like management and communication but also advanced skills like setting issues and solving problems.

ation control / Information leak control / Information security literacy

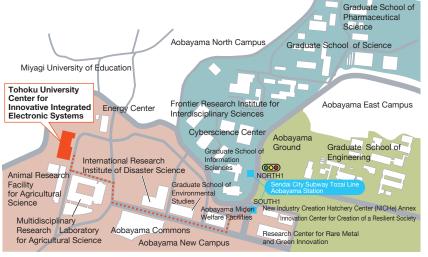

## Access

### By Subway

Please take subway Tozai Line bound for "Yagiyama Zoological Park Station" from "Sendai Station", and get off subway at "Aobayama Station". (about 9 mins ride) Please go out from Exit South 1, and it is about 10 minutes' walk from "Aobayama Station" to CIES.

## Contact

### Tohoku University Center for Innovative Integrated Electronic Systems

468-1 Aramaki Aza Aoba, Aoba-ku, Sendai, Miyagi 980-8572, JAPAN TEL: +81-22-796-3410 FAX: +81-22-796-3432 E-mail: support-office@cies.tohoku.ac.jp HP: http://www.cies.tohoku.ac.jp/english/ 2023.3